HOME > OFDM IP

OFDM IP

- 特長

- OFDM IPカタログ PDF

- スクラッチ実装

- MATLAB/Simulinkモデルからのコード生成

- フルカスタマイズ可能

- 提供形態

- ソースコード

- MATLAB/Simulinkモデル

- コード生成ライセンス

- ネットリストまたはバイナリ

- 特許

- OFDM IP開発当初(2000年代前半),キーワードを用いた特許検索を行ってます。

- 以後,特許調査は行っていませんが,自社開発コード以外は参照していません。

- 開発から10年以上経過しており,国内大手企業の納入実績がありますが,特許の問題が生じたことはありません。

- 開発ツール

- OFDM IPは開発ツールRDEおよびRDEを用いたOFDMシステムのコンポーネントからなります。

- RDEは専用のMATLAB/SimulinkブロックセットおよびHDL生成ツールからなります。

- 現在のところ32bit版MATLABのみサポートします。MATLABを実行するOSは64bitもサポートします。

- HDLソースコードはMATLAB/SimulinkモデルからHDL生成ツールによって生成されます。

- 現在のところVHDLのみ生成可能です。

- 生成されたソースコードは一部命名方法が機械的ですが,可読です。

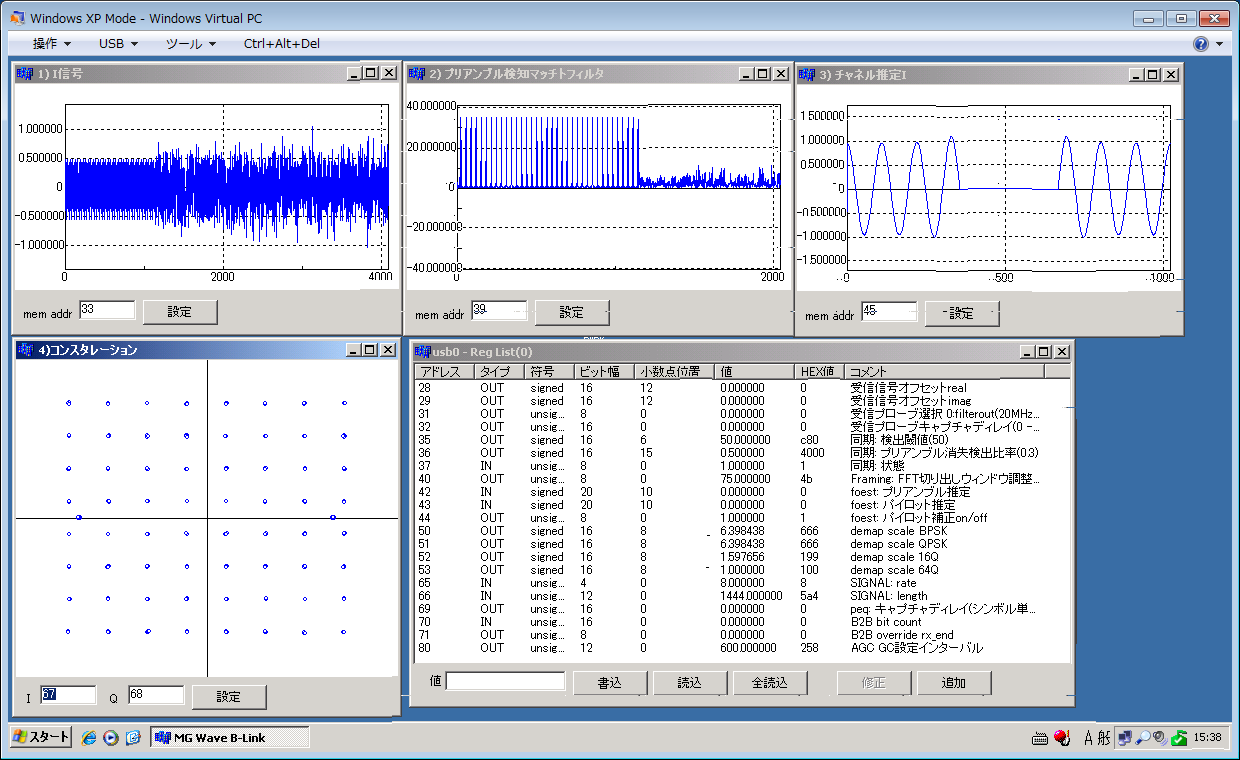

- SPI-Likeなシリアル通信により,FPGA実機の内部をモニタ可能です。(費用別途)

- 詳細仕様書

- RDEを用いる開発では一般的なHDL開発のような詳細仕様書を省略可能です。

- MATLAB/Simulinkモデル自体がいわば動く詳細仕様書になっています。

- 入出力信号のフォーマットやタイミング波形をモデルから読み取ることができます。

- HDLシミュレーション

- RDEを用いる開発では一般的な一般的なHDLシミュレーションを省略可能です。

- RDEが生成するHDLコードとMATLAB/Simulinkモデルの等価性はコード生成ツールによって担保されています。

- HDLシミュレーションが必須の場合は,ModelSim向けのテストベンチをご用意できます。(費用別途)

- 論理合成ツール

- RDEを用いる開発では論理合成ツールとしてSynplify Pro K-2015.09-SP1を用います。

- RDE開発当時,ISEやQuartusの論理合成性能が十分ではなく,実行不可能な回路を合成する場合があり,実用に耐えなかったためです。

- 最新のVivadoやQuartusでの合成検証は現在のところ未実施です。

- サポート

- 納品から1年間のサポート期間を標準としています。

- 納品状態のHDLコードおよびMATLAB/Simulinkモデルの動作や使用方法に関する質疑応答を想定しています。

- 担当の情報共有のため,メール等の文書のやり取りが基本です。

- 実機試験やデバッグも受託可能です。(費用別途)

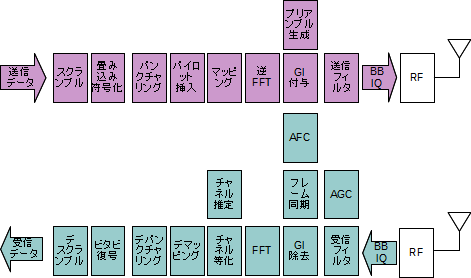

設計例

- 802.11a

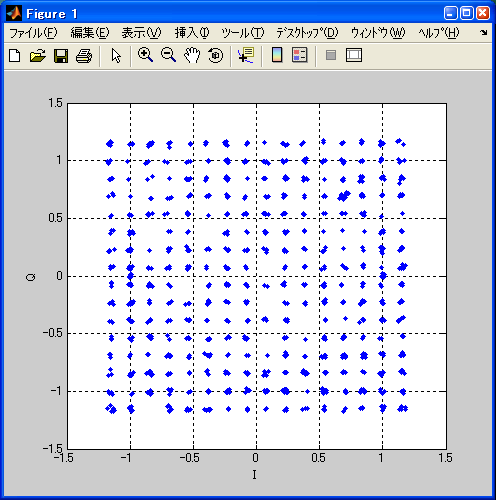

- 512点FFT, 256QAMを用いた独自システム

| FFT点数 | Nfft = 64 |

|---|---|

| FFTサンプル周波数 | Fs = 20MHz |

| サブキャリア間隔 | Cs = Fs / Nfft |

| 有効シンボル長 | Tse = 1 / Cs |

| ガードインターバル | Tgi = Tse / 4 |

| シンボル長 | Ts = Tgi + Tse |

| データサブキャリア数 | Ndsc = 48 |

| パイロットサブキャリア数 | Npsc = 4 |

| DCサブキャリア数 | Ndc = 1 |

| 帯域幅 | Bw = Fs * (Ndsc + Npsc + Ndc) / Nfft |

| ショートプリアンブル長 | 16 / Fs * 10 |

| ロングプリアンブル長 | (1/2 + 2) * Tse |

| 変調・符号化方式 | BPSK-1/2, BPSK-3/4, QPSK-1/2, QPSK-3/4, 16QAM-1/2, 16QAM-3/4, 64QAM-2/3, 64QAM-3/4 |

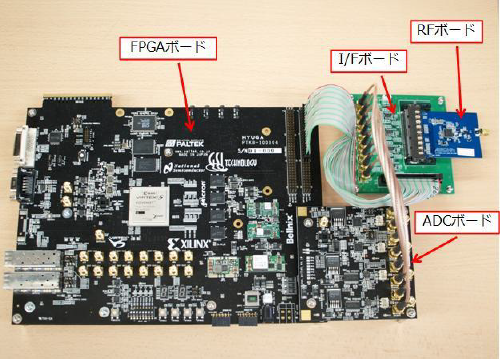

ハードウェア開発・評価

- ハードウェア設計や実機評価も受託可能です。

- 実機試験の様子。奥は暗室。

![]()